|

|

Главная » Микропроцессорное управление 1 ... 4 5 6 7 8 9 10 ... 27 BMl- c o-JJDo- 1 \ЗПр

Ulo-

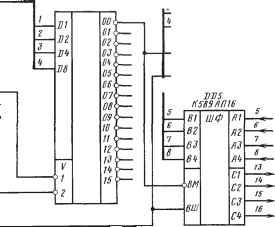

Рис. 2.9. Схема МБР К589ИР12 Таким образом, данные на ШФ могут поступать по четырехразрядным шинам А или В, а выдаваться по четырехразрядным шинам В или С соответственно. Выбор направления передачи данных осупхествляется с помощью сигнала, подаваемого на вход ВШ. Микросхема шинного формирователя К589АП26 отличается от вышеописанной только тем, что сигналы на выходах В и С инвертируются по отношению к сигналам на входах А i\ В соответственно. Многорежимный буферный регистр (МБР) представляет собой универсальный 8-разрядный регистр, выходные каскады которого имеют три устойчивых состояния. Регистр снабжен схемами управления режимами и формирования сигнала запроса на прерывание и предназначен для реа;шзации многих типов интерфейсных и вспомогательных устройств, включая буферные регистры, мультиплексоры, двунаправленные шинные формирователи, прерываемые каналы ввода - вывода и т. д. Многорежимный буферный регистр (рис. 2.9) состоит из восьми информационных тактируемых 1)-триггеров, восьми выходных ключей (К) с тремя устойчивыми состояниями ( О , 1 , состояние с высоким выходным сопротивлением), 1)-триггера для формирования запроса на прерывание (ЗПр) и схемы управления режимами работы триггера. Входные данные поступают на информационные входы DO-D7, а считываются через ключи с выходов 0 - Q7. Многорежимный буферный регистр имеет следующие управляющие входы: ВМ1, ВМ2 - входы выбора микросхемы; ВР- вход выбора режима; С- стробирующий вход; R - вход установки в состояние О . В режиме считывания ключи К передают информацию на выходы Q0 - Q7, если выполняется условие 4T=BPV (ВМ1ЛВМ2)=1, где ЧТ- значение двоичного сигнала на управляющих входах ключей; ВР - значение двоичного сигнала на одноименном входе; ВМ1, ВМ2 - значения двоичных cnrnajwB на одноименных входах; Л - операция логического умножения И; V -операция логического сложения ИЛИ^ Примечание: (ВМ1ЛВМ2)=1 является условием выбора микросхемы (кристалла). Для того чтобы это условие выполнялось, необходимо на вход ВМ1 подать уровень логического О , а на ВМ2 -уровень логической 1 . Если ЧТ = 0, то ключи К находятся в состоянии с высоким выходным сопротивлением, что соответствует отключению МБР от выходной щины, и считывания информации не происходит. Режим записи информации в МБР осуществляется при вьшолнении условия ЗП = (СЛВР) V (ВМ1ЛВМ2ЛВР)=1, где ЗП-значение двоичного сигнала на тактирующих входах £)-триггеров; С-значение двоичного сигнала на одноименном входе МБР. Если на вход С подан уровень логической 1 , а на вход ВР-уровень логического О и условие выбора микросхемы не выполняется, то (СЛВР)=1, ЗП = 1, ЧТ = 0, т.е. осуществляется только запись информации без считывания. При выполнении условия (ВМ 1 Л ВМ2Л ВР)= 1, ВР=1, ЗП=1, ЧТ= 1 происходит запись информации с одновременным считыванием, т. е. информация с входов DO - Dl передается на выходы Q0 -Q1 МБР. Установка информационных триггеров в состояние О обеспечивается входным сигналом R = 0. С помощью отдельного £)-триггера и управляющей логики в МБР формируется сигнал запроса на прерывание ЗПр, активным уровнем которого является уровень логического О . Условие формирования сигнала ЗПр = 0; П 589 ИРП ЛЧ V5 ю с

Рис. 2.10. Графическое обозначение многорежимного буферного регистра От вУ ПВ-Л7 \ и,- BdiSop ВУ +SB о- CrnpoS ввода Cffpoc К Mfl В0-В7 Выбор ВУ о- серое <}ВМ1 вмг вр с 1± МЕР QD-U7 ЗПр1> ti МП

ao-u7 Рис. 2.11. Примеры использования МБР К589ИР12: а-ввод информации; 6-вывод информации i?C V (ВМ1 л ВМ2)=1, которое выполняется либо при выборе микросхемы (ВМ 1 Л ВМ2) = 1, либо при С=1 и R-\. Сброс сигнала запроса на прерывание (ЗПр=1) осундествляется при условии R ЛВМ1ЛВМ2 = которое выполняется, если i? = 0 и (ВМ1ЛВМ2) = 0. Графическое обозначение многорежимного буферного регистра, выполненного в виде интегральной микросхемы К589ИР12, представлено на рис. 2.10. Примеры организации интерфейсов в МПСУ. На рис. 2.11 показаны примеры использования многорежимного буферного регистра (K589MP12J) в устройствах ввода-вывода информации. в режиме ввода информации (рис. 2.11 ,а) данные от внешнего устройства (ВУ) поступают на информационные входы DO-D7. На вход ВР подается уровень логического О , поэтому запись в данных в МБР произойдет только при подаче строба ввода на вход С (ЗП = (СЛВР)=1). При С=1 на выходе МБР устанавливается сигнал запроса на прерывание ЗПр = 0. Если микропроцессор выставляет на шину адреса ША код адреса внешнего устройства, с которым связан данный МБР, то на вход ВМ1 с дешифратора адреса подается уровень логического О . Выполняется условие выбора микросхемы (ВМ1ЛВМ2) = 1. Происходит считывание данных с выходов Q0- Q7 МБР. Данные по шине данных ШД поступают в МП. Микропроцессор снимает код адреса ВУ с шины адреса. Выходные каскады МБР переходят в состояние с высоким выходным сопротивлением. Многорежимный буферный регистр отключается от ШД и цикл ввода заканчивается. При записи новых данных цикл ввода повторяется. В режиме вывода информации (рис. 2.П,б) на вход ВР подается уровень логической 1 (ЧТ=1), поэтому выходные каскады МБР находятся в активном состоянии, и информация с выходов Q0-Q7 постоянно поступает к ВУ. Запись новой информации в МБР осуществляется посредством выбора микросхемы. Для этого МП выставляет на ША код адреса ВУ и с дешифратора адреса на вход ВМ1 поступает уровень логи- ка/-?; лиг

или К155ЛИ1 & ЛЛд И155ИДЗ ЛЛЦ-H589flnW  Рис. 2.12. Схема подключения устройств ввода-вывода к системной магистрали Й-41 ческого О (BMl Л ВМ2= 1). Выполняется условие ЗП = ВМ1 ЛВМ2ЛВР=1, и информация с ШД поступает на входы DO-D7 и заносится в регистр. На этом цикл вывода информации заканчивается. При необходимости вывести новые данные цикл вывода повторяется. Рассмотрим схему подключения устройств ввода - вывода к системной магистрали И-41 (рис. 2.12). Схема позволяет подключить к магистрали до 64 УВВ. Дешифратор DD2 (К155ИД4) служит для выбора дешифратора адреса DD3 (К155ИДЗ). Другие дешифраторы адреса (на схеме не показаны) подключаются к выходам 51,2,3 микросхемы DD2. Сигналы с дешифратора адреса DD3 используются как сигналы ВМ шестнадцати буферов ввода - вывода информации, в качестве которых используются шинные формирователи ШФ К589АП16. Входные по отношению к микропроцессору сигналы подключаются ко входам А\-А 4 микросхем DD4, DD5. а выходные ~к выходам С1 -С4. Входы - выходы В\-В4 этих микросхем подключаются к ШД. Следует заметить, что информация на выходах С1 - С4 сохраняется лишь во время выдачи сигнала ВМ, а после его снятия выходы переходят в третье состояние. 2.3. УСТРОЙСТВА СВЯЗИ С ОБЪЕКТОМ Как правило, устройство связи с объектом выполняется в виде различных модулей, например модуля обмена с оптронной развязкой (МОО), модуля приема аналоговых сигналов (МПА), модуля выдачи дискретных (МВД) и аналоговых (МВА) сигналов и т. п. Преобразователи напряжения в код с компенсационным интегрированием. Из всех видов АЦП наибольшее распространение имеют преобразователи напряжения в код (ПНК). В микроэлектронике для преобразования аналоговых напряжений, снимаемых с различных датчиков, широко используются интегрирующие ПНК последовательного счета, обеспечивающие высокие помехоустойчивость и точность. Как правило, на детерминированные сигналы, снимаемые с датчиков, накладываются различного рода шумы или помехи, представляющие собой случайные процессы. В качестве характеристики зашумленности сигнала в технике используется отношение сигнал - шум. Если спектральные характеристики сигнала и шума различны, то эффективным способом повышения отношения сигнал-шум является метод аналогового интегрирования сигналов. При реализации этого метода происходит накопление полезного сигнала, а шумы и помехи частично компенсируются. Интегрирующие ПНК обычно строятся по методу компенсационного интегрирования, впервые предложенного советскими 68

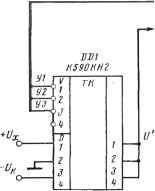

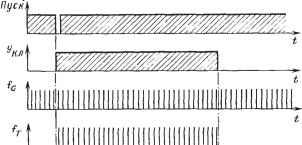

yt \уг\ уз\ [т,-1]\. (0*1)1 Рис. 2.13. Структурная схема ПНК с компенсационным интегрированием типа напряжение - временной интервал - код инженерами В. Г. Беляковым и Е. В. Добровым в 1960 г. Рассмотрим обобщенную структурную схему ПНК с компенсационным интегрированием типа напряжение-временной интервал код (рис. 2.13). Преобразователь напряжения в код содержит следующие элементы: коммутатор аналоговых напряжений DD 1, интегратор, схему сравнения (СС), формирователь импульсов (ФИ), устройство управления (УУ), генератор импульсов (G), ключ и двоичный счетчик (СТ2) с входом установки в состояние - О (R). В качестве коммутатора аналоговых напряжений рационально использовать микросхему К590КН2, представляющую собой четыре независимых токовых ключа с дискретным управлением (ключ открыт, если на его управляющий вход V подается уровень логического О ). На управляющие входы ключей поступают сигналы У1, У2, УЗ с устройства управления. На информационные входы ключей поступают преобразуемое напряжение -\-U ОВ ( Земля ) и компенсирующее напряжение - U. Информационные выходы всех ключей объединены и связаны с входом аналогового интегратора, выполненного на операционном усилителе. Временные диаграммы сигналов в рассматриваемом ПНК представлены на рис. 2.14. В исходном состоянии открыт ключ 2 {DDI). На вход интегратора поступает напряжение f/ = 0B. Напряжение на выходе интегратора = U. В момент времени /о на устройство управления поступает сигнал Пуск . На вход интегратора подается положительное постоянное напряжение U= +U. Это напряжение интегрируется в течение фиксированного интервала времени = /j - = 2 т, где л - число разрядов (выходов) счетчика СТ2; 2 - число внутренних состояний этого счетчика; х - период следования импульсов Д.

Рис. 2.14. Временные диаграммы сигналов в ПНК с компенсационным интегрированием типа напряжение - временной интервал-код В начале временного интервала счетчик СТ2 устанавливается в нулевое состояние сигналом, подаваемым на вход R. Одновременно открывается ключ DDI и на тактовый вход счетчика С поступают импульсы j\ с генератора импульсов G. Конец временного интервала (момент времени определяется либо по переполнению счетчика (состоянию, при котором на всех его выходах-логические 1 ), либо по переходу О в 1 на дополнительном (и+1) выходе счетчика. В момент на вход интегратора подается отрицательное постоянное напряжение {7= - t/. абсолютное значение которого выбирается заведомо большим, чем абсолютное значение U. Это напряжение интегрируется в течение интервала времени T = t2 - ti=Nx, где - число импульсов, сосчитанных на интервале Т^. При равенстве напряжений и формирователь Таблица 2. 2. Формулы для определе-яяя напряжения на выходе интегратора импульсов ФИ формирует импульс F, который поступает на вход УУ и служит для идентификации момента tj. В момент времени ключ DD2 закрывается, а на вход интегратора поступает напряжение и =0В. В этот момент заканчивается цикл преобразования. На выходах счетчика СТ2 фиксируется код числа п - 1 N= 2;, где fl;-логический уровень сигнала на / °-м выходе счетчика; 2 - вес разряда счетчика. Покажем, что число Л^ импульсов, сосчитанных на временном интервале Г^., пропорционально измеряемому напряжению U. Напряжение на выходе интегратора определяется по формуле

Udt, (2.1) где -постоянная времени интегратора; t-текущее время (г^Го)> -напряжение на входе интегратора. . Значения напряжений на выходе интегратора в фиксированные моменты времени t, и можно определить по (2.1) (табл. 2.2). При t = t2 справедливо равенство 2 U.dt=U,. (2.2) Учитывая, что на интервале интегрирования С/ = const и U = = const, получаем Ah-to)=Ah-h) или UJ, = UJ. Подставляя в последнюю формулу Т^ = 2 х и T = Nx, находим f/. = t. = E 24. (2.3) Принцип компенсационного интегрирования используется также при построений ПНК типа напряжение-частота-код (рис. 2.15, fl), главная составная часть которого-преобразователь напряжения в частоту (ПНЧ) представляет собой замкнутую систему автоматического регулирования частоты. вл1 - иное Dm - НПВЛА7 vvj - кткл ла - кпбтиг ввг  Рис. 2.15. Преобразоватспь напряжения в код с компенсационным интегрированием типа напряжение -частота - кол : а структурная схема ПНК; б врематые диаграммы сигналов ПНК Постоянное напряжение через аналоговый ключ DD3 поступает на вход интегратора, выполненного на операционном усилителе (ОУ), на второй вход которого поступает импульсное напряжение [/ с выхода ПНЧ. Напряжение U с выхода интегратора поступает на вход схемы сравнения (СС), на второй вход которой подается опорное напряжение Ug. В momcftt равенства напряжений U и на выходе формирователя импульсов (ФИ) формируется импульс Uf с амплитудой U, длительность которого постоянна и равна т. Кроме ПНЧ, выполненного на базе интегральной микросхемы DDI, схема ПНК содержит ключи DD2 и DD3, iiS-Tpnrrep и двоичный счетчик СТ2, с помощью которого реализуется преобразование частоты в код. При подаче импульса Пуск , который соответствует началу временного интервала Tq, счетчик СТ2 устанавливается в состоя-72 ние О , а триггер DD4 - в состояние 1 , в результате чего открываются ключи DD2 и DD3. На вход интегратора поступает напряжение U, а на вход счетчика - импульсы Uf. При подаче импульса КПр (конец преобразования), соответствующего концу временного интервала Tq, триггер DD4 устанавливается в состояние О , закрываются ключи DD2, DD3 и на выходе счетчика фиксируется двоичный код, пропорциональный преобразуемому напряжению U. Рассмотрим (рис. 2.15, б), как изменяется напряжение на выходе интегратора в течение временного интервала Г (периода следования импульсов Uf). В течение времени т на суммирующие входы интегратора поступают напряжения и U, противоположные по знаку. Причем значение выбрано таким, что I к11 .xmaxl, где \ - абсолютнос значение напряжения U; \Uxmax\ - максимальное абсолютное значение напряжения U. На интервале времени - полярность напряжения на инверсном входе ОУ определяется полярностью U, а на интервале ?2~i -полярностью U. Поэтому в течение времени т напряжение на выходе интегратора линейно убывает, а в течение времени (Т^ - х) линейно возрастает. По аналогии с (2.2) получаем Udt=Uo. (2.4) о о Учитывая,- что (7., = const и (7 = const. Отсюда с использованием формулы (2.4) получаем где /. - частота следования импульсов Uf. Число импульсов, сосчитанных на интервале Tq, равно N=TJ, и f,N/To. Используя последние формулы, находим и^=и^х^-=и^2%. (2.5) Отметим свойства ПНК с компенсационным ингегрированием: 1. Код на выходе ПНК пропорционален входному напряжению и^. 2. В результирующих формулах (2.3) и (2.5) отсутствует член поэтому медленные вариации эквивалентной постоянной времени Г„ не сказываются на точности преобразования, если Г„ не изменяется в течение интервала времени Т^.

|

Как выбрать диван  История мебели  Стили кухонной мебели  Публикации  Инверторы  Приемники |

|||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||